#### $7\sim$ 11GHz

# key indicator

- $\square$  Frequency range: 7 $\sim$ 11GHz

- ☐ Gain: 23dB

- ☐ Noise figure: 1.1dB@9GHz typical value

- Output P\_1 dB: 18.5dBm@9GHz typical value

- Chip size: 1.47mmx1.25mmx0.1mm

## typical application

- ☐ Satellite communications

- ☐ Test measurement

- Optical fiber communication

#### **Product Introduction**

AY1644 works in 7 $\sim$ 11GHz and is made of GaAs process. Under 29mA working current, it can provide 23dB gain, 18.5dBm output P-1dB, and the noise in the normal temperature band is lower than 1.1dB.

The chip uses an on-chip metallization process to ensure good grounding, and the back of the chip is metallized, which is suitable for eutectic sintering or conductive adhesive bonding processes.

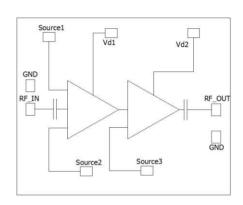

#### Functional block diagram

Electrical performance ( $T_A=25^{\circ}\text{C}$ , $V_{d1}=V_{d2}=+5V$ , $I_{d1}=28\text{mA}$ , $I_{d2}=29\text{mA}^{[5]}$ , $Z_0=50\Omega$ ,)

| index                     | Minimum | Typical value | Max | unit |

|---------------------------|---------|---------------|-----|------|

| Frequency Range           |         | 7 ~ 11        |     | GHz  |

| Gain                      | -       | 22/23 [1]     | -   | dB   |

| Input return loss         | -       | 14            | -   | dB   |

| Output return loss        | -       | 14            | -   | dB   |

| Noise figure @9GHz        | -       | 1.2 / 1.1 [2] | -   | dB   |

| Output P <sub>-1</sub> dB | -       | 16 / 18.5 [3] | -   | dBm  |

| Gain flatness             | -       | 1             | -   | dB   |

# Absolute maximum rating

| Maximum input power | +5dBm | Operating temperature | -55 ℃ ~ + 85 ℃    |

|---------------------|-------|-----------------------|-------------------|

| Channel temperature | 150 ℃ | Storage temperature   | -65 °C ∼ + 150 °C |

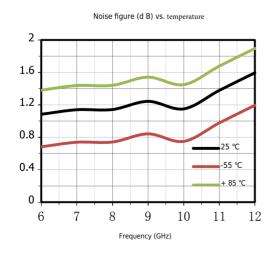

$[1] LNA \ bias \ at \ Vd1=3V, ld1=36mA, \ \ Vd2=4V, ld2=54mA (Source \ 1/2/3 \ connect \ to \ GND \ are \ required). which \ gives \ the \ highest \ Gain \ (Source \ 1/2/3 \ connect \ to \ GND) \ are \ required). Which \ gives \ the \ highest \ Gain \ (Source \ 1/2/3 \ connect \ to \ GND) \ are \ required). Which \ gives \ the \ highest \ Gain \ (Source \ 1/2/3 \ connect \ to \ GND) \ are \ required). Which \ gives \ the \ highest \ Gain \ (Source \ 1/2/3 \ connect \ to \ GND) \ are \ required). Which \ gives \ the \ highest \ Gain \ (Source \ 1/2/3 \ connect \ to \ GND) \ are \ required). Which \ gives \ the \ highest \ Gain \ (Source \ 1/2/3 \ connect \ to \ GND) \ are \ required). Which \ gives \ the \ highest \ Gain \ (Source \ 1/2/3 \ connect \ to \ 1/2/3 \ conne$

$[2] LNA \ bias \ at \ Vd1=3V, Id1=27mA, \ \ Vd2=4V, Id2=28mA (Source\ 1\ connect\ to\ GND\ are\ required). which \ gives\ the\ lowest\ noise\ figure \ (Connect\ to\ GND\ are\ required). The property of the lowest\ to give the lowest\ noise\ figure\ (Connect\ to\ GND\ are\ required). The property of the lowest\ noise\ figure\ (Connect\ to\ GND\ are\ required). The property of the lowest\ noise\ figure\ (Connect\ to\ GND\ are\ required). The property of the lowest\ noise\ figure\ (Connect\ to\ GND\ are\ required). The property of the lowest\ noise\ figure\ (Connect\ to\ GND\ are\ required). The property of the lowest\ noise\ figure\ (Connect\ to\ GND\ are\ required). The property of the lowest\ noise\ figure\ (Connect\ to\ GND\ are\ required). The property of the lowest\ noise\ figure\ (Connect\ to\ GND\ are\ required). The property of the lowest\ noise\ figure\ (Connect\ to\ GND\ are\ required). The property of the property of the lowest\ noise\ figure\ (Connect\ to\ GND\ are\ required). The property of the property of the lowest\ noise\ figure\ (Connect\ to\ GND\ are\ required). The property of the$

$[3] LNA\ bias\ at\ Vd1=3V, Id1=15mA,\ \ Vd2=6V, Id2=58mA\ (Source\ 3\ connect\ to\ GND\ are\ required). which\ gives\ the\ highest\ PdB$

[4]LNA bias at Vd1=3V,Id1=15mA, Vd2=4V,Id2=28mA (None of Source pad connect to GND are required

$\label{eq:connect} \ensuremath{\texttt{LNA}} \ \ \text{bias at Vd1=5V,Id1=28mA}, \ \ \ \text{Vd2=5V,Id2=29mA} \ \ \ \ \ \ \ \text{Cource 1 connect to GND are required)}.$

1

7∼11GHz

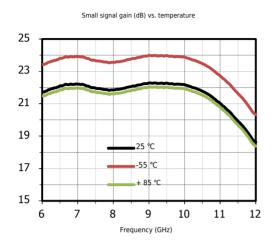

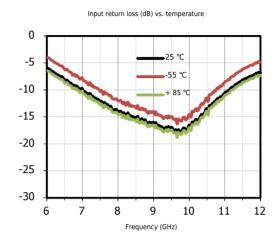

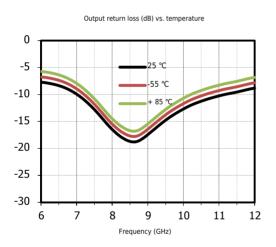

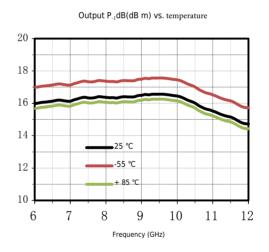

# Typical test curve

$(V_{d1} = 5V, I_{d1} = 28mA, V_{d2} = 5V, I_{d2} = 29mA^{[5]})$

7∼11GHz

# Typical test curve

$7\sim$ 11GHz

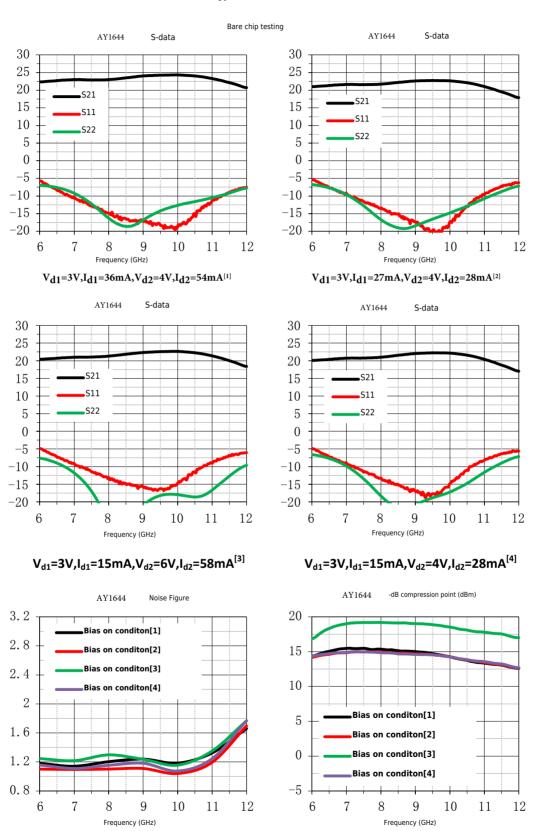

# Shape and port size (mm)

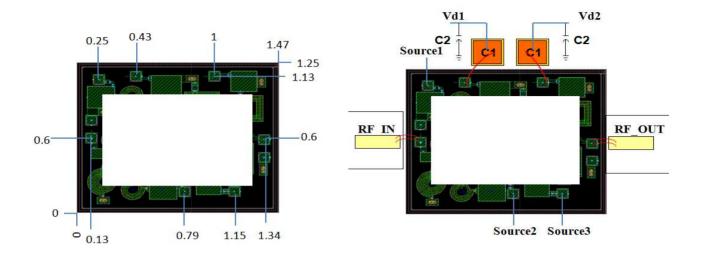

# Recommended assembly drawing

#### Assembly table

| Pad                               | connect                                                                 |

|-----------------------------------|-------------------------------------------------------------------------|

| V <sub>d1</sub> , V <sub>d2</sub> | Self-biased structure, both nodes must be connected to the power supply |

| Source 1/2/3                      | Adjustable node for adjusting noise/gain/P <sub>-1</sub> dB             |

## **Component list**

| C1 | 330pF | 116RM331M050TT     | ATC    | -    |

|----|-------|--------------------|--------|------|

| C2 | 10nF  | GRM155R71H103KA88D | MURATA | 0402 |

# Precautions

- 1. The chip is stored in a dry, nitrogen environment and used in an ultra-clean environment;

- 2. GaAs material is relatively brittle and cannot touch the surface of the chip, so you must be careful when using it;

- 3. Chips are sintered with conductive glue or alloy (the alloy temperature cannot exceed 300°C, and the time cannot exceed 30 seconds) to make it fully grounded;

- 4. The gap between the microwave port of the chip and the substrate should not exceed 0.05mm. Use Φ25μm double gold wire for bonding. The recommended length of gold wire is 250~400μm:

- gold wire for bonding. The recommended length of gold wire is  $250{\sim}400\mu m$ ; 5. The chip is sensitive to static electricity, so pay attention to anti-static during storage and use.